外部维度上,移动终端与HPC系统对性能、能效、散热及微型化提出了近乎苛刻的要求。这驱动着行业探索从单芯片封装向异构系统集成跃迁。

晶圆级封装(WLP)与晶圆级系统集成(WLSI)技术在此背景下脱颖而出。依托晶圆级工艺的规模化优势,WLSI平台通过低成本、超薄化与高集成度的解决方案,重新定义了系统级整合的边界。

其技术突破集中体现为两大方向:其一,深度摩尔定律(More Moore)路径下,通过先进封装实现逻辑芯片的晶体管密度持续微缩;其二,超越摩尔定律(More than Moore)路径中,将CMOS芯片与非硅基功能单元(如传感器、光电器件)异构集成,构建单器件级多功能系统。这一模式转变已催生出集成扇出(InFO)等标志性技术,成为移动计算领域的主流方案,并逐步向HPC场景延伸。

晶圆级扇入封装技术

晶圆级封装(WLP)作为先进封装技术的核心分支,通过直接在晶圆上完成封装工艺,实现了系统微型化与成本优化的双重突破。

其技术体系包含扇入型(Fan-In)与扇出型(Fan-Out)两大变体,本文仅聚焦扇入型WLP的技术特征与工程实践。

封装结构与工艺流程

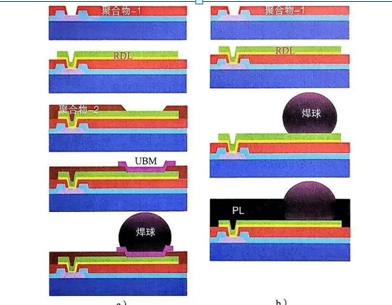

扇入型WLP采用"芯片级封装"架构,所有BGA焊球直接布局于硅芯片有效投影面积内,无需额外基板或转接板。典型工艺流程包含四步:

钝化保护与RDL布线:在完成晶圆表面钝化后,通过物理气相沉积(PVD)制备钛/铜种子层,电镀铜形成再布线层(RDL),实现芯片I/O端口从密集焊盘区向封装表面的扇入扩展;

介电层成型:采用聚酰亚胺(PI)或聚双苯并恶唑(PBO)等光敏聚合物构建介电层,经光刻工艺形成互连通孔与布线沟槽;

UBM制备:通过电镀或化学镀工艺沉积凸点下金属化层(UBM),常用材料包括铜、镍或ENEPIG合金,形成与BGA焊球的冶金结合界面;

焊球植入与切割:在晶圆级完成BGA焊球植球后,进行晶圆切割获得单颗封装器件。

该工艺流程的精简性赋予扇入型WLP三大优势:封装体尺寸与芯片尺寸1:1等比、工艺步骤较传统封装减少40%-60%、制造周期缩短至2-3天。

关键材料与结构优化

介电层设计:通过调节聚合物厚度(通常5-20μm)平衡机械缓冲与工艺精度。较厚介电层可缓解硅-PCB间热膨胀系数失配(CTE mismatch)引发的热应力,但会增加光刻通孔成型难度;

RDL层级扩展:单层铜布线可满足常规需求,双层RDL结构通过增加铜厚(≥5μm)提升机械可靠性,使芯片适用尺寸扩展至10mm×10mm级别;

UBM成本管控:铜基UBM方案较传统镍/金体系成本降低30%-50%,但需优化掩模数量(通常2-4层)以平衡工艺复杂度与良率。

可靠性挑战与突破路径

热循环测试表明,硅-PCB界面CTE差异(硅4.3ppm/K vs. PCB 17ppm/K)导致的剪切应力是主要失效机理,具体表现为:

尺寸效应:芯片边长超过8mm时,BGA焊球疲劳寿命呈指数下降;

应力缓解方案:通过三维结构优化实现应力分散:

增加封装体高度(BGA球高≥0.3mm)提升中性点距离(DNP);

采用柔性聚合物材料(模量<2GPa)构建可变形缓冲层;

优化UBM焊盘形貌(圆形/环形设计)改善应力分布。

大尺寸芯片封装实现

工程实践证实,通过协同优化材料体系与结构设计,可实现边长达25.4mm(1英寸)的大尺寸扇入型WLP。

关键技术包括:

复合缓冲结构:采用"介电层/RDL/UBM"三层复合缓冲,将热循环寿命提升至1000次以上;

焊球强化技术:通过颈部聚合物包覆(Underfill Encapsulation)使焊球抗剪强度提升40%;

制造良率管控:在6mm×6mm以下尺寸可保持99%以上良率,8mm×8mm器件需引入缺陷检测与激光修复工艺。

当前行业实践显示,扇入型WLP在消费电子领域形成标准化方案,而10mm×10mm以上尺寸则需权衡工艺成本与可靠性裕度,这推动了扇出型WLP在高性能计算领域的迭代发展。